ts_top_tx_mpw fts_top_tx_mpw(

.clk : in std_logic;

.reset : in std_logic;

.c_reset : in std_logic;

.c_reset_out : out std_logic;

.da_out_i : out std_logic_vector(7 downto 0);

.da_out_q : out std_logic_vector(7 downto 0);

.dac_clk_i : out std_logic;

.dac_clk_q : out std_logic;

.wrt_out_i : out std_logic;

.wrt_out_q : out std_logic;

위와 같은 VHDL 코드가 있을 경우,, (Port Instance를 쉽게하기위하여 .을 미리 붙여준다. 물론 Ctrl+q . [ESC] 를 이용하여,, 또는 : 앞의 포트이름만 선택해서 .을 붙여줘도 좋을듯하다.)

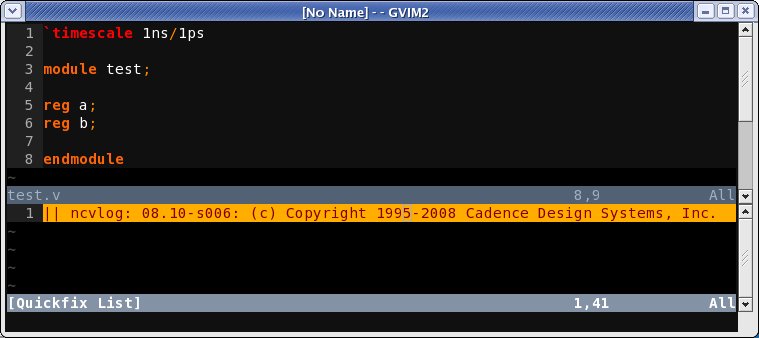

%s/\.\(\([a-zA-Z_0-9]\)*\)\s*:\s*\([a-zA-Z0-9_" "();]\)*/\.\1(p_\1),/g

하면,,

ts_top_tx_mpw fts_top_tx_mpw(

.clk(clk),

.reset(reset),

.c_reset(c_reset),

.c_reset_out(c_reset_out),

.da_out_i(da_out_i),

.da_out_q(da_out_q),

.dac_clk_i(dac_clk_i),

.dac_clk_q(dac_clk_q),

.wrt_out_i(wrt_out_i),

.wrt_out_q(wrt_out_q),

로 바꿔준다. ^_^ ㅋㅋㅋ

7,39s/\.\(\([a-zA-Z_0-9]\)*\)\s*:\s*\(\([a-zA-Z0-9_" "();]\)*\)/\.\1(tx_\1),\t\t\/\/\3/g

ts_top_tx_mpw fts_top_tx_mpw(

.clk(tx_clk), //in std_logic;

.reset(tx_reset), //in std_logic;

.c_reset(tx_c_reset), //in std_logic;

.c_reset_out(tx_c_reset_out), //out std_logic;

---------------------------------------

.da_out_i(tx_da_out_i), //out std_logic_vector(7 downto 0);

.da_out_q(tx_da_out_q), //out std_logic_vector(7 downto 0);

.dac_clk_i(tx_dac_clk_i), //out std_logic;

.dac_clk_q(tx_dac_clk_q), //out std_logic;

.wrt_out_i(tx_wrt_out_i), //out std_logic;

.wrt_out_q(tx_wrt_out_q), //out std_logic;